- TOP

- リンクステックのつよみ

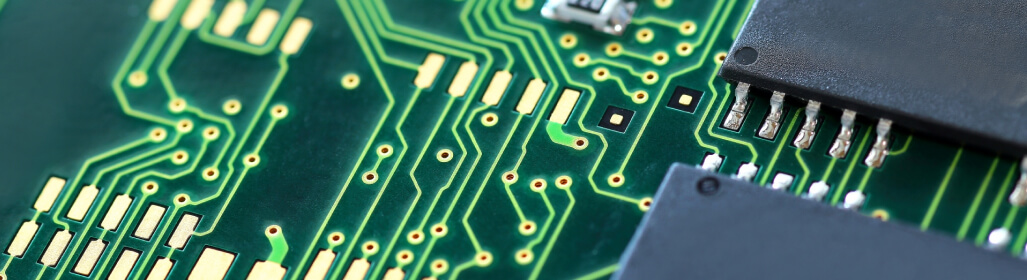

- スマートフォンの小型化と回路設計の自由度拡大を実現した、表裏実装可能な配線板

Development Story1

スマートフォンの

小型化と回路設計

の自由度拡大を

実現した、表裏

実装可能な配線板

The introduction of

substrate has導入成果

- 製品の回路設計の自由度が高まった

- 製品の小型化を実現した

- 製品の接続信頼性向上

- スマホ主力製品に搭載され、

業界における技術進展に貢献した

Background of development開発背景

高い接続信頼性や高密度実装の

特性を活かした

表裏実装モジュール開発をしたい

近年、スマートフォンの内部に使用される部品の多機能化や、モジュール部品の小型化が急速に進んでいます。こういったモジュール部品の技術的課題は、電子部品の実装領域を「いかに小さくするか」にあり、この分野での技術革新が求められています。その中で注目されていたのが、表裏実装を可能にしたプリント配線板の開発です。

「高い接続信頼性や高密度実装の特性を活かした、表裏実装用モジュール基板の開発が出来ないだろうか?」「そうすれば、これまで以上にモジュール用基板が小型化でき、お客様の回路設計の自由度も高めることができる。」「これまでに無い、新しい回路デザインの可能性を広げられるはずだ。」 その想いが製品開発のきっかけでした。

Problems and solutions課題と解決策

最初の課題は

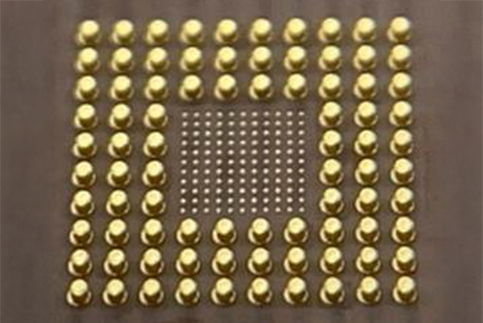

バンプピッチの高密度化

これまで表裏実装を可能にしてきたモジュールには、システムインパッケージがあります。しかしそれは、外部端子接続用端子にはんだを用いていました。はんだボール径やはんだパッド径の制約から外部端子接続用端子ピッチの高密度化が困難でした。

そこで開発担当者は、表裏実装が可能な銅バンプ付きプリント配線板の開発に着目します。

バンプピッチだけでは解消できない

次の課題は、銅バンプ形成のプロ

セスの見直し

開発初期段階で作成したサンプルでは、銅バンプとパッド電極間の優れた密着は改善できたものの、バンプの高さのばらつきが大きい状態でした。

このままでは「すべてに優れたレベルの表裏実装モジュールの高密度化」は実現が難しく、主な要素技術であるめっきプロセスの見直しが必要となりました。

解決のカギは、配線板の種別を

問わない

全てのノウハウの統合

リンクステックは、これまで進めてきたモジュール基板の開発で、外部端子形成可能な層間接続用のフィルドめっき技術や、高アスペクト比のめっき技術を培ってきました。

開発担当者は、これらリンクステックが培ってきた技術を改良し組み合わせることで、これまで実現出来なかった「表裏実装用基板の高密度化」を可能にすることができるのではないかと考え、開発を進めました。上記の様々な要素技術をベースに、最適な銅バンプ形成プロセスを開発することで、お客様の回路設計自由度を高める事ができる表裏実装モジュールが完成しました。